Advanced IC packaging is a hot new hotbed of competition between AI processor manufacturers and other advanced integrated circuit ( IC ) manufacturers, and it’s emerging as the next frontier in the US government’s efforts to lessen America’s dependence on foreign suppliers and halt China’s technological advancement.

However, unlike “front-end” IC wafer fabrication, where US sanctions have seriously constrained China’s advance, “back-end” assembly, packaging and test ( APT ) is an area where China has a large market presence and sophisticated technology, making it relatively immune to US technology blocks.

Taiwan’s TSMC, by far the world’s largest and most technologically advanced IC foundry, is rapidly expanding its Chip-on-Wafer-on-Substrate ( CoWoS ) packaging capacity. This will end a offer barrier that has kept Nvidia, AMD, and Intel’s most recent AI processors manufactured at procedure nodes below 5 micrometers.

Huawei has used its own Circuit design and presentation technologies to move above the performance cap the US Commerce Department has set on Nvidia cards that can be sold it, which has so far been unable to drop below 5 nm due to the ban on selling ASML’s EUV printing chip-making systems to China.

Especially, Huawei’s new Ascend 910C computer, which was see commercial shipping within the next two decades, apparently outperforms Nvidia’s dumbed-down H20.

Tom’s Hardware writes,” According to Huawei, the device is on par with Nvidia’s H100, but it is unclear]on ] which benchmark terms the Ascend 910C is comparable to Nvidia’s previous-generation flagship product”. ExtremeTech calculates that, overall, the H20 has” 28 % less AI performance” than the H100.

Even if Huawei is overstating its capabilities, it appears to have made sufficient progress to throw Nvidia, AMD, and Intel in danger of losing their Artificial computer jobs in the Chinese business.

Without any outside competition, Huawei and other Chinese manufacturers could have what is likely to be the largest marketplace for these devices entirely on their own.

Use of equipment created and manufactured in China today makes it simpler and less risky for Alibaba, Baidu, ByteDance, China Mobile, Tencent, and another Chinese clients who would have preferred to purchase the more sophisticated US-designed chips.

The US Commerce Department perhaps impose tighter sanctions and make it accessible to China, just like it would with any US-designed device. Even if Chinese ICs are less effective or ready, the shift is being accelerated by this uncertainty.

Meanwhile, data from business solutions reported by tech media websites in Taiwan and elsewhere indicate that regular production of ICs using TSMC’s CoWoS, technology does more than double to 40, 000 units by the end of this year, boost by 50 % to 60, 000 in 2025 and achieve 80, 000 by the end of 2026.

CoWoS is , a 2.5-dimensional ( 2.5D ) packaging technology developed by TSMC for high-performance ICs used in computing, data centers and telecom equipment. As can be seen in the diagram below, it utilizes through-silicon via ( TSV ) vertical electrical connections and a silicon interposer.

According to Cadence Design Systems, a leading electronic design automation company, CoWoS “is particularly well-suited for artificial intelligence ( AI ) accelerators, where multiple types of chips need to work together efficiently” – including high-bandwidth memory ( HBM ).

AMD noted that” HBM is a new type of memory device with ultra-wide contact lanes and low energy consumption.” It uses horizontally stacked memory cards that are connected by microscopic wires known as through-silicon vias, or TSVs.

Cadence explains that” 2.5D packaging … is an intermediate step between traditional 2D packaging and full-fledged 3D packaging. In 2.5D package, many silicon dies, usually from various approach technologies, are placed side by side on a silicon interposer. The interposer acts as a bridge, connecting the individual dies and providing a high-speed communication interface”.

This “enables the integration of diverse components, such as processors, memory, and sensors, on a single package. This proximity results in shorter interconnects, which in turn improve signal integrity and latency.

In addition, it reduces both the size of the package and power consumption and facilitates heat dissipation.

As it ramps up CoWoS production capacity, TSMC should be able to catch up with the backlog of orders for Nividia’s H100 processors and be ready to roll out its new Blackwell B200 processors, expected to start early next year.

According to NextBigFuture’s Brian Wang, the B200 is 25 times more efficient and four times faster than the H100. It wo n’t be known until the middle of the year what users and analysts will think of Huawei’s overall AI performance, but it significantly raises the bar. However, it will almost certainly not be sold in China.

The first CoWoS version was released by TSMC in 2012. As recently reported in a Chinese news site Guancha ( Observer Net ) article, Huawei’s IC design division HiSilicon” conducted a comprehensive assessment of CoWoS in 2014, including cost and yield, and decided to take the lead” in adopting the technology.

Starting with the integration of 16nm logic chips and 28nm Input-Output ( I/O ) chips, Huawei HiSilicon worked with TSMC all the way to 7nm in 2019. That advancement came to an end in 2020 when the US fined Huawei and ordered TSMC to stop.

However, Huawei already had years of experience putting the idea into practice, which refers to the components that come together in a system-on-chip as” chiplets” in general. AMD, Apple, Intel and Nvidia all use chiplet design. IBM explains it as follows:

The goal of chiplets is to break up the system on a chip into its composite functional blocks, or parts. Sub-elements of a complex-function chip could be made as chiplets, where these sub-elements might include separate computational processor or graphics unit, an AI accelerator, an I/O function, or a host of other chip functions. A system comprised of chiplets is kind of like an SoC on a module, and, in the future, could be made using interoperable mix-and-match chiplet components sourced from multiple providers. This approach could lead to chiplets powering entirely new computing paradigms, creating more energy-efficient systems, shortening system development cycle time, or building purpose-built computers for less than it would cost today.

Huawei/HiSilicon has reportedly amassed hundreds of patents covering chiplet technology. In 2021, Shenzhen-based Chipuller acquired 28 from failed Silicon Valley venture company Glue.

Chipuller CEO Yang Meng told Reuters that, with chiplets,” US-China competition is on the same starting line. In other ( chip technologies ) there is a sizeable gap between China and the United States, Japan, South Korea, Taiwan”.

However, chiplets allow the Chinese to bypass the US’s trade restrictions on advanced semiconductor production equipment, which have so far prevented them from getting beyond 5 nm.

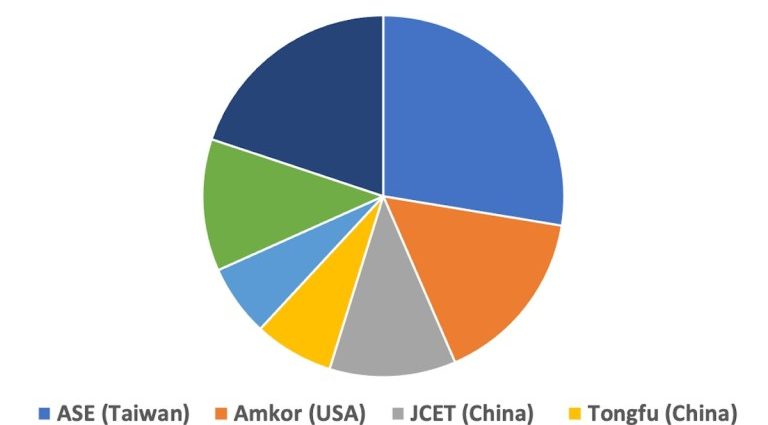

China has a very advanced and significant IC packaging sector. Two of the world’s top five outsourced semiconductor assembly and test ( OSAT ) companies – JCET, which ranks third, and Tongfu Microelectronics, which ranks fourth – are Chinese, while Beijing ESWIN and other smaller companies are also developing chiplet technology.

Tongfu is unique because it has worked with AMD for many years and jointly runs joint-venture factories in Suzhou and Penang.

The Chinese government believes that advanced IC packaging in general and chiplets in particular are essential for overcoming US sanctions and establishing a competitive and independent Chinese semiconductor sector.

The US government, which also regards advanced IC packaging as crucial, plans to subsidize the construction of Amkor’s first OSAT facility in the US. Amkor, the world’s second-largest OSAT company, is based in Arizona.

US Commerce Secretary Gina Raimondo stated in late July that “one of the fundamental goals of the CHIPS and Science Act is creating an advanced packaging ecosystem in the US to ensure full start to finish chip production occurs domestically.” These technologies will be the foundation of global economic and national security for decades to come.

According to reports, the Biden administration has been considering enforcing a ban on exporting chip assembly and packaging equipment to China in response to China hawks in Congress. However, it does n’t seem to have made much progress so far, perhaps because the majority of the equipment is produced in Japan.

Japan has reportedly objected to the most recent US request to enforcing sanctions against China, but the Chinese are reportedly taking no chances. In addition to advanced packaging processes, they are developing their own dicing, wire bonding, test and other assembly, packaging and test equipment.

With more than 20 leading Japanese materials and equipment companies, TSMC is developing advanced 3D packaging technology at its Japan 3DIC R&, D Center, which is located in the science city of Tsukuba northeast of Tokyo.

While the US frets about Chinese chiplets, they are switching from 2.5D CoWoS to 3D technology to prepare for smaller process nodes that are already being developed.

Follow this writer on , X: @ScottFo83517667